# **AX206**

# **Digital Photo Frame SoC** Product Specification

Rev 1.1.0 Jun 2009

www.appotech.com

| AppoTech Limited |                                             |

|------------------|---------------------------------------------|

| Address          | : Unit 705-707, 7/F, IC Development Centre, |

|                  | No. 6, Science Park West Ave.               |

|                  | Hong Kong Science Park,                     |

|                  | Shatin, N.T. Hong Kong                      |

| Telephone        | : (852) 2607 4090                           |

| Fax              | : (852) 2607 4096                           |

# AX206 8-bit RISC Microcontroller

#### High Performance 8-bit RISC MCU

- DC-48MHz operation, 48MIPS (Max 48MHz)

- Compatible with 8051

- Fetch 1 instruction byte in 1 cycle

#### **Program Memory and Data Memory**

- 4K Bytes Mask-ROM program memory

- 3K Bytes internal data SRAM (Also use as IRAM and USB FIFO)

#### **Interrupt Features**

- External wakeup/interrupt capabilities on 3 GPIO and USB PHY

- 2-level interrupt priority

#### Flexible I/O

- 35 GPIO pins in 5 ports

- All GPIO pins can be individually programmable as input or output

- All GPIO pins are internal pull-up selectable

- TTL-level inputs with Schmitt Trigger

- All GPIO pins are 6mA current output driving except 4 GPIO pins are 12mA current output driving

#### **Digital Peripheral Features**

- One 8-bit timer: Timer 0

- Two multi-function 16-bit timers: Timer 1 and Timer 2, support PWM mode

- Real-time wake up

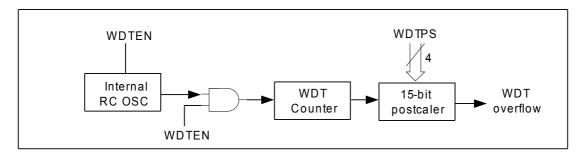

- Watchdog Timer with on-chip 16KHz RC Oscillator

- Full-speed USB 2.0 controller and PHY module with 2 endpoints (including endpoint 0). USB FIFO Share with IRAM

- One high-speed SPI, Maximum throughput 24Mb

- One UART

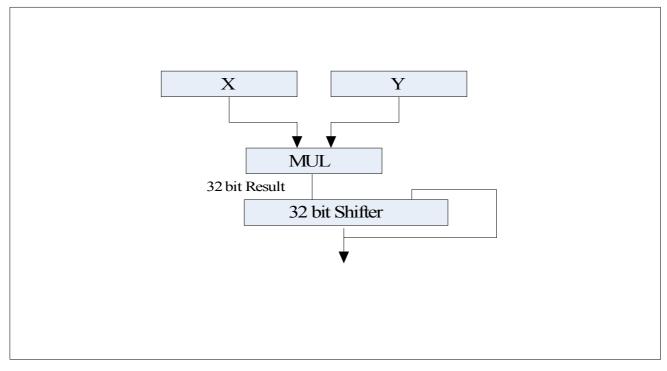

- 16-bit x 16-bit Multiplier for IDCT

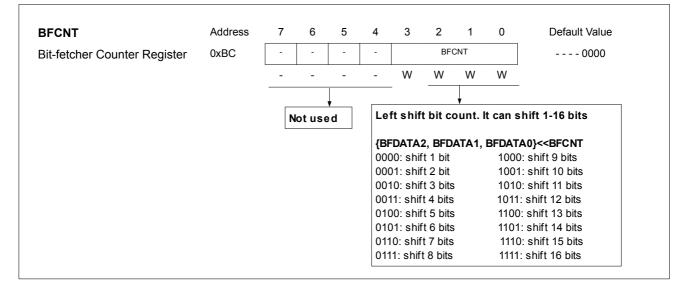

- Bit-fetcher for Huffman Decode

#### **Analog Peripheral Features**

- External 24MHz Oscillator

- Internal 16KHz RC Oscillator

- Real-Time Clock Oscillator (32.768KHz)

- Frequency doubler

- 8 Channel 10-bit ADC

- Power-on Reset

- BOR Reset

- LDO

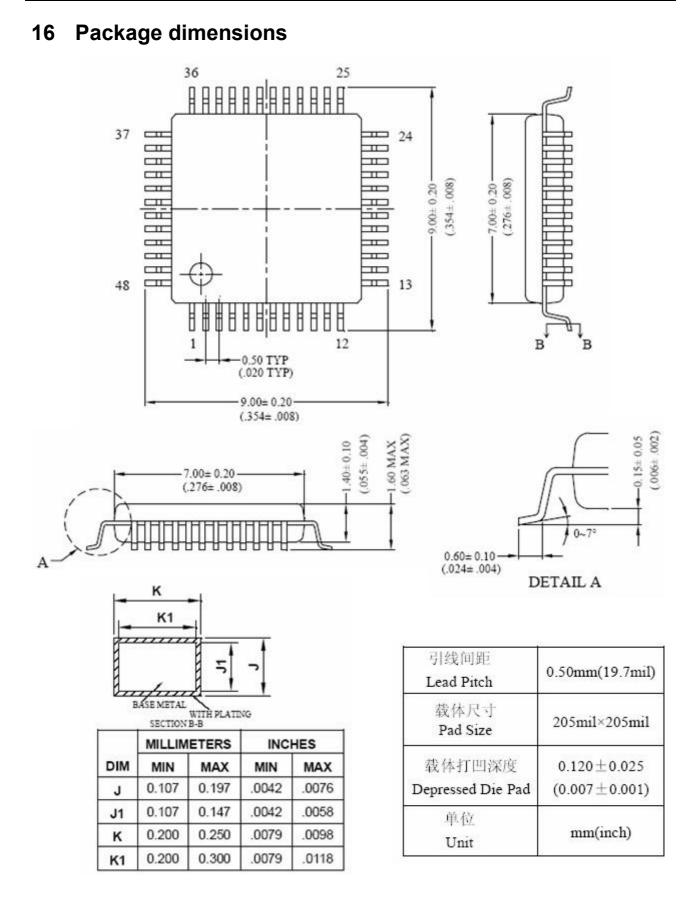

#### **Packages**

- 48-pin LQFP (7mm x 7mm)

- DIE form

#### AppoTech Limited

| Appoicon    |                                            |

|-------------|--------------------------------------------|

| Address     | :Unit 705-707, 7/F, IC Development Centre, |

|             | No.6, Science Park West Ave.,              |

|             | Hong Kong Science Park,                    |

|             | Shatin, N.T., Hong Kong                    |

| Telephone   | :(852) 2607 4090                           |

| Fax         | :(852) 2607 4096                           |

| www.appotec | h.com                                      |

|             |                                            |

# **Table of Contents**

| Chapter | 1   | Product Overview                                  | .6 |

|---------|-----|---------------------------------------------------|----|

|         | 1.1 | Description                                       | .6 |

|         | 1.2 | System Architecture                               | .7 |

| Chapter | 2   | Pin Information                                   | .8 |

|         | 2.1 | Pin Assignment                                    |    |

|         |     | 2.1.1 LQFP48                                      |    |

|         |     | 2.1.2 Pin Description                             | .9 |

| Chapter | 3   | Memory Mapping and CPU Architecture               | 11 |

|         | 3.1 | Basic Structure                                   | 11 |

|         | 3.2 | Interrupt Entry Address Mapping                   | 12 |

|         | 3.3 | Data Memory – DRAM (DATA)                         | 13 |

|         | 3.4 | General Purpose Register (REGISTER)               | 13 |

|         | 3.5 | Extended Data Memory – XRAM (XDATA)               | 13 |

|         | 3.6 | CPU Instruction Set Summary                       |    |

|         |     | 3.6.1 Basic Instruction Set                       | 14 |

| Chapter | 4   | Special Function Register (SFR)                   | 18 |

|         |     | SFR List                                          |    |

|         |     | CPU and Interrupt SFR                             |    |

| _       |     | ·                                                 |    |

| Chapter |     | Interrupt Processing                              |    |

|         |     | Interrupt Sources and Vectors.                    |    |

|         |     | Interrupt Priorities                              |    |

|         | 5.3 | Interrupt Latency                                 | 26 |

| Chapter | 6   | Clocks and Reset Management                       | 27 |

| -       |     | Clock System                                      |    |

|         |     | 6.1.1 Clock Source Control                        |    |

|         |     | 6.1.2 Clock Gating Control.                       |    |

|         |     | <ul><li>6.1.3 Oscillator configurations</li></ul> |    |

|         |     | 6.1.5 RC Oscillator                               |    |

|         | 6.2 | Reset System                                      |    |

|         |     | 6.2.1 Reset Sequence                              |    |

|         |     | 6.2.2 Master Reset                                | 32 |

|         |     | 6.2.3 Power On Reset.                             |    |

|         | ~ ~ | 6.2.4 Watchdog Timeout Reset                      |    |

|         | 0.3 | Power Management                                  | 33 |

|            | 6.3.1 Operating in 3.3V or 5V Systems                                     |    |

|------------|---------------------------------------------------------------------------|----|

|            | 6.3.2 Idle Mode<br>6.3.3 Halt Mode                                        |    |

|            | 6.3.4 Power Down Mode                                                     |    |

|            |                                                                           |    |

| Chapter 7  | Ports                                                                     | 36 |

| 7.         | 1 Registers                                                               | 37 |

|            | 2 Interrupt and Wakeup                                                    |    |

|            | 3 Operation Guide                                                         |    |

| Chapter 8  | Multi-Function Timer                                                      | 44 |

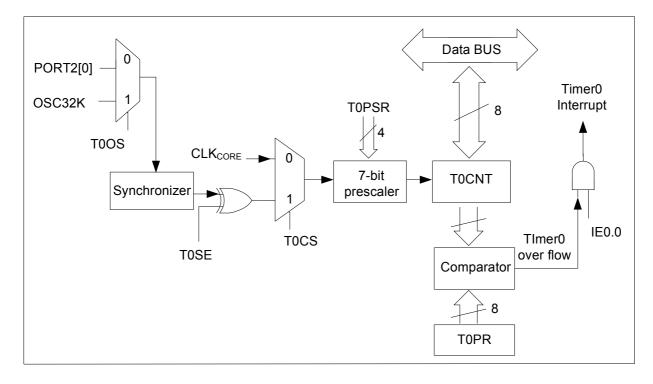

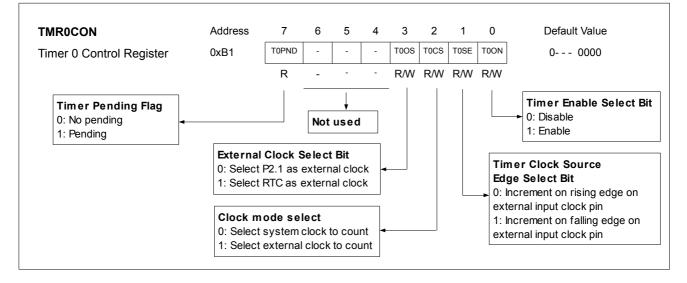

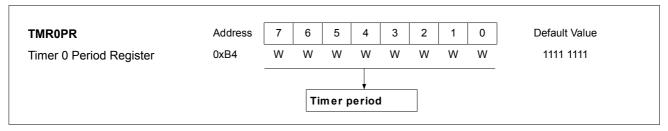

| 8.         | 1 Timer0                                                                  | 44 |

|            | 8.1.1 Timer0 Registers                                                    | 45 |

|            | 8.1.2 Operation Modes                                                     |    |

|            | 8.1.3 Interrupt                                                           |    |

|            | 8.1.4 Operation Guide                                                     |    |

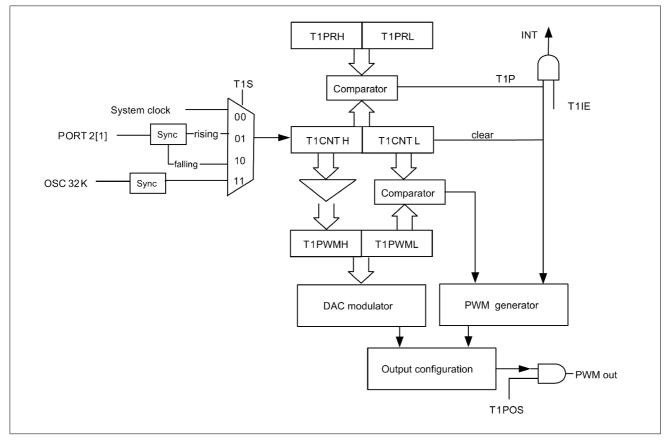

| 8.         | 2 Timer1                                                                  |    |

|            | 8.2.1 Timer1 Registers                                                    |    |

|            | 8.2.2 Timer1 Operation Mode                                               |    |

|            | 8.2.3 Interrupt<br>8.2.4 Operation Guide                                  |    |

| 0          | •                                                                         |    |

| 8.         | 3 Timer2                                                                  |    |

|            | 8.3.1 Timer2 Register<br>8.3.2 Operation Mode                             |    |

|            | 8.3.3 Interrupt                                                           |    |

|            | 8.3.4 Operation Guide                                                     |    |

| 8          | 4 Watchdog Timer with On-chip 16kHz RC oscillator                         |    |

| 0.         | 8.4.1 Watchdog Timer Register                                             |    |

|            | 8.4.2 Operation Mode                                                      |    |

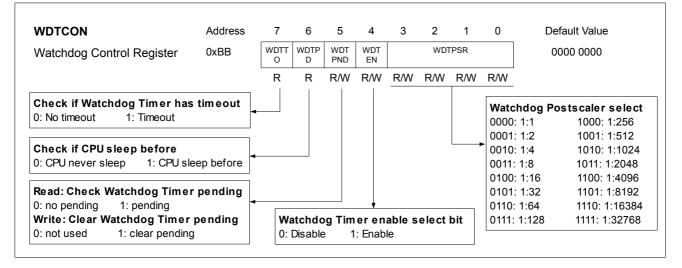

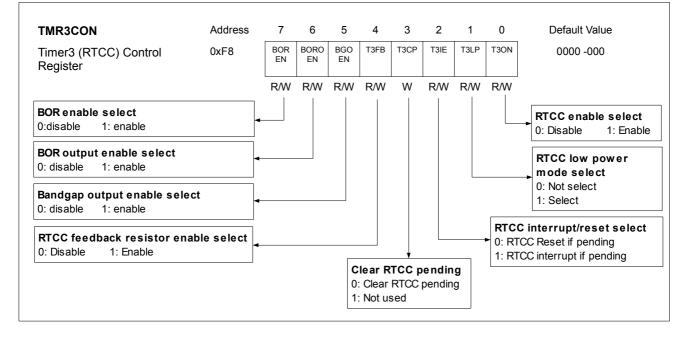

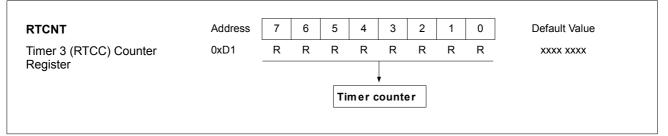

| 8          | 5 RTCC Timer                                                              |    |

| 0.         | 8.5.1 RTCC Timer Register                                                 |    |

|            | 8.5.2 Operation Mode                                                      |    |

|            | 8.5.3 Operation Guide                                                     |    |

| Chapter 9  | Serial Protocol Interface (SPI)                                           | 59 |

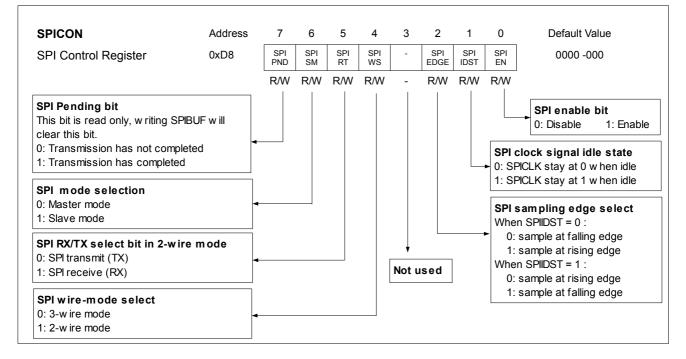

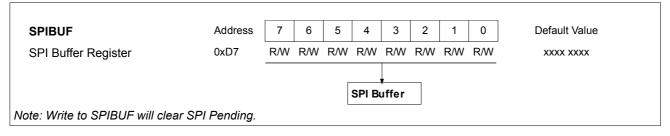

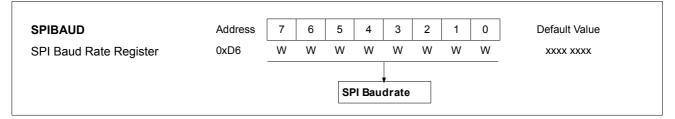

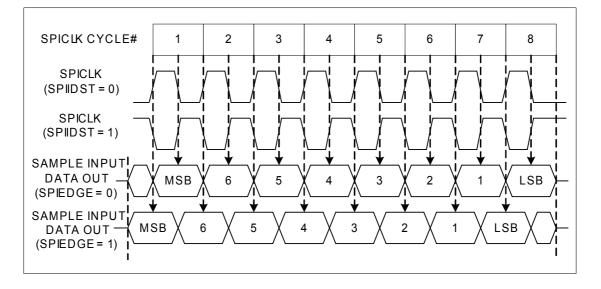

| 9.         | 4 SPI Registers                                                           | 59 |

|            | 5 Baudrate Setting                                                        |    |

|            | 6 Operation Mode                                                          |    |

|            | 7 Operation Guide                                                         |    |

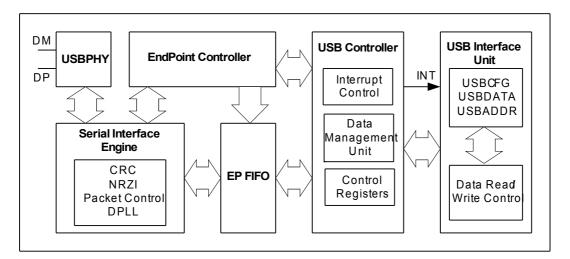

| Chapter 10 | USB Device Controller and PHY                                             |    |

| -          | 0.1 Registers                                                             |    |

|            |                                                                           |    |

| П          | 0.2 Operation Mode<br>10.2.1 Registers Read From/Writer to USB Controller |    |

|            | 10.2.2 Control The USB Module                                             | 64 |

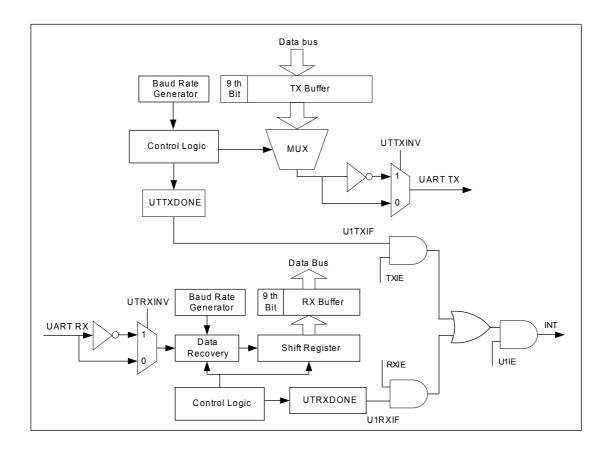

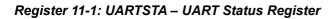

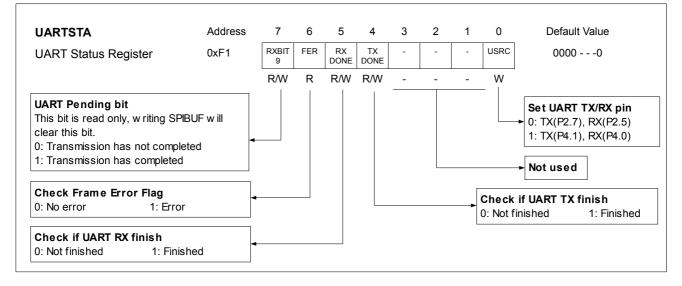

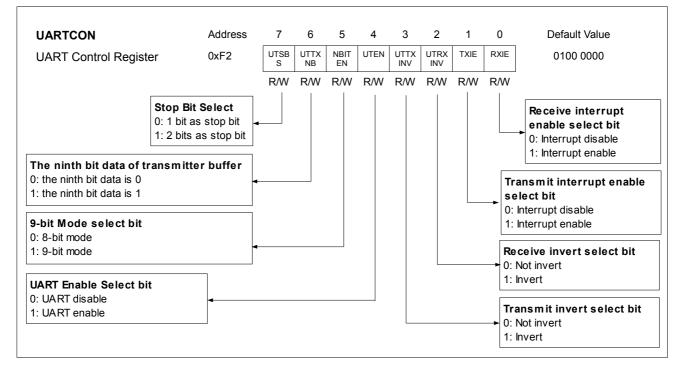

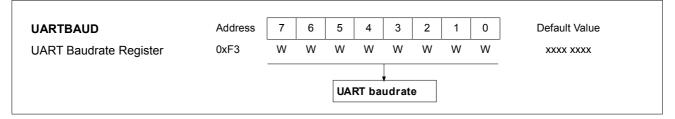

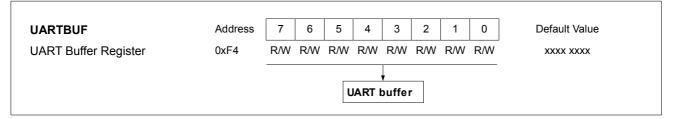

| Chapter 11  | UART                             | .66 |

|-------------|----------------------------------|-----|

| 11.         | .1 Registers                     | .67 |

| 11.         | .2 Operation Guide               | .68 |

|             | 11.2.1 UART TX Operation Flow    |     |

|             | 11.2.2 UART RX Operation Flow    | .68 |

| Chapter 12  | 16-bit x 16-bit Multiplier (MUL) | .70 |

| 12.         | .1 Registers                     | 71  |

| 12.         | .2 Operation Guide               | .73 |

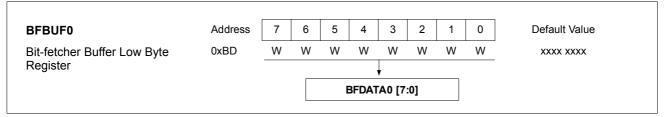

| Chapter 13  | Bit-Fetcher                      | .74 |

| 13.         | .1 Registers                     | .74 |

|             | .2 Operation Guide               |     |

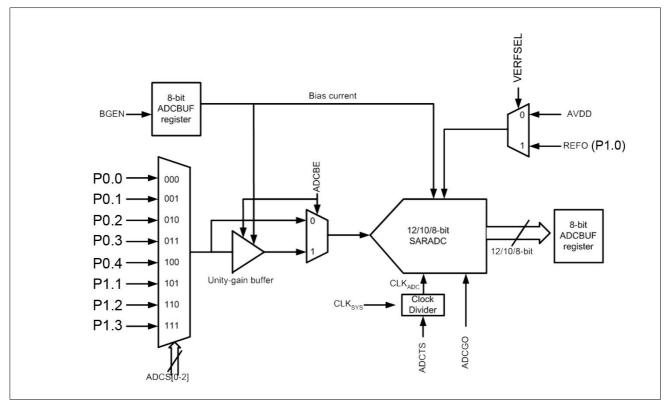

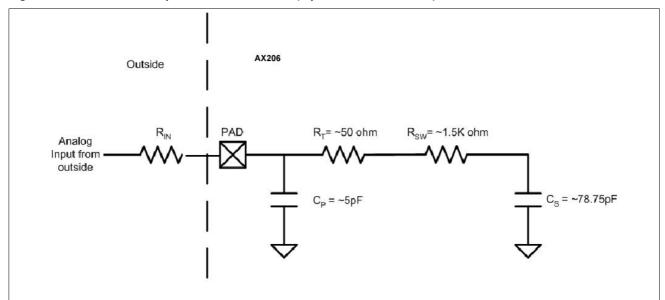

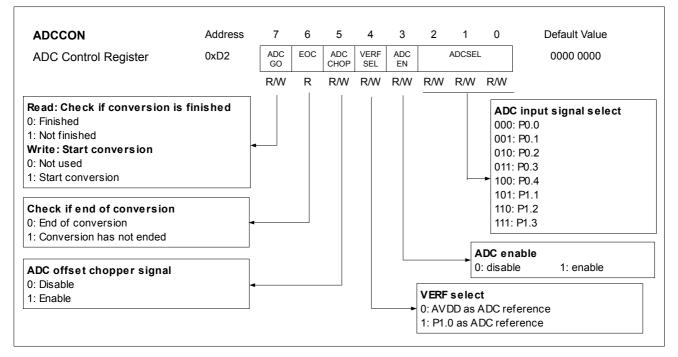

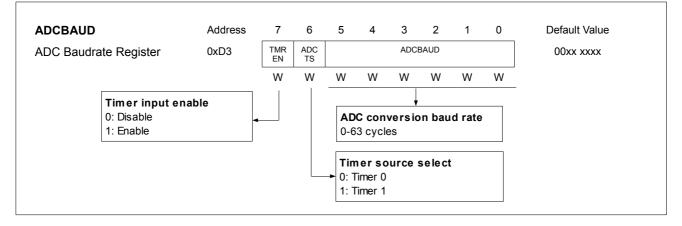

| Chapter 14  | ADC                              | .76 |

| -           | .1 ADC Architecture              |     |

|             | .2 Registers                     |     |

|             | .3 Operation Guide               |     |

| Chapter 15  | Electrical Characteristics       | .80 |

| -           | .1 Absolute Maximum Rating       |     |

|             | .2 DC Characteristics            |     |

|             | .3 AC Parameters                 |     |

| Chapter 16  | Package dimensions               | .83 |

| Appendix I  | Revision History                 | .84 |

| Appendix II | I USB Function Register          | .85 |

## **1** Product Overview

### 1.1 Description

AX206 is an 8051 compatible high performance mixed signal 8-bit microcontroller. It integrates advanced digital and analog peripherals to suit for a variety of applications.

The AX206 has the following features:

- 8-bit RISC CPU compatible with 8051

- Fetch 1 instruction byte in 1 cycle

- CPU can run in RTC (32.768K), 12MHz, 24MHz or 48MHz. (External oscillator is 24MHz)

- 4K bytes Mask ROM Program Memory

- 3K bytes SRAM which can be used as XDATA and Program Memory (IRAM).

- External Wakeup/Interrupt capabilities on 3 GPIO and USB PHY

- 2-level interrupt priority

- 35 GPIO pins in 5 ports (P0, P1, P2, P3, P4)

- All GPIO pins can be individually programmable as input or output

- All GPIO pins are internally pull-up selectable

- ALL GPIO pins are 6mA current output driving except 4 GPIO pins are 12mA current output driving

- Full-Speed USB 2.0 controller and PHY module with 2 endpoints. USB shares part of SRAM

- A high-speed SPI and a high-speed UART

- 16-bit x 16-bit Multiplier for IDCT

- Bit-Fetcher for Huffman Decode

- 8 Channel 10-bit ADC

- Power-on Reset and BOR

- LDO

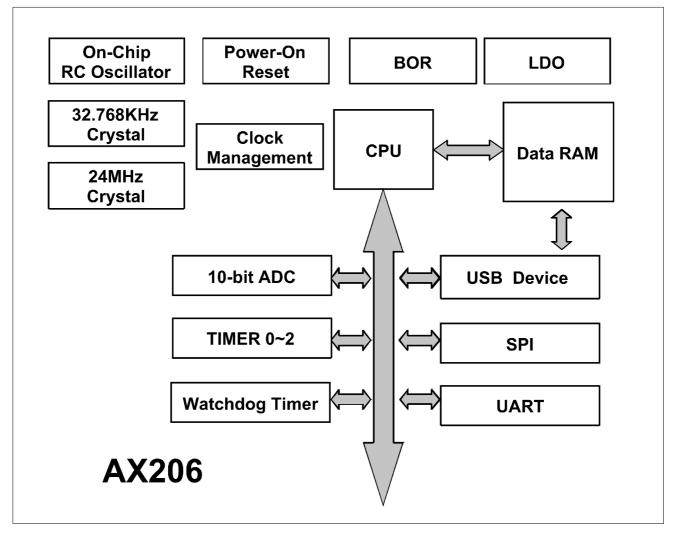

### 1.2 System Architecture

Figure 1-1: System Architecture

### 2 Pin Information

### 2.1 Pin Assignment

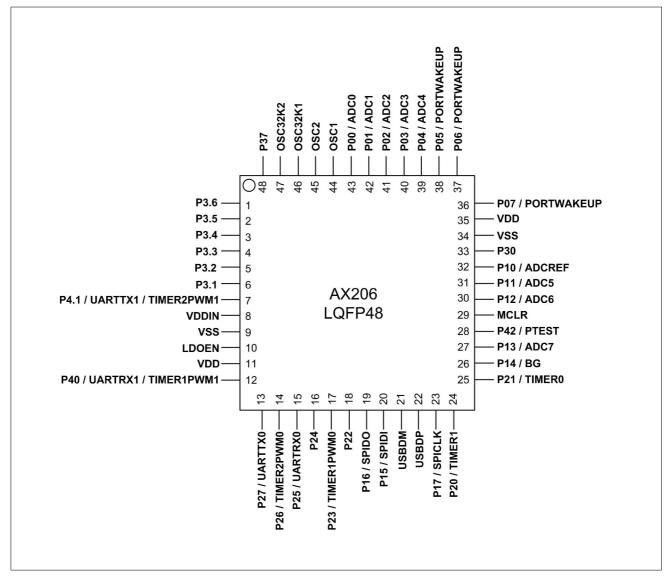

### 2.1.1 LQFP48

#### Figure 2-1: LQFP48 Pin Assignment

### 2.1.2 Pin Description

### Table 2-1: Pin Description

| Pin | Symbol          | Direction | Description                   |

|-----|-----------------|-----------|-------------------------------|

| 1   | P36             | I/O       | Port 3 pin 6                  |

| 2   | P35             | I/O       | Port 3 pin 5                  |

| 3   | P34             | I/O       | Port 3 pin 4                  |

| 4   | P33             | I/O       | Port 3 pin 3                  |

| 5   | P32             | I/O       | Port 3 pin 2                  |

| 6   | P31             | I/O       | Port 3 pin 1                  |

| 7   | P41 / UARTTX1 / | I/O       | Port 4 pin 1                  |

|     | TIMER2PWM1      | 0         | UART TX1                      |

|     |                 | 0         | Timer2 PWM1 Output            |

| 8   | VDDIN           | Power     | LDO 5.0V Input                |

| 9   | VSS             | Ground    | VSS                           |

| 10  | LDOEN           | I         | LDO Enable                    |

| 11  | VDD             | Power     | 3.3V                          |

| 12  | P40 / UARTRX1 / | I/O       | Port 4 pin 0                  |

|     | TIMER1PWM1      | I         | UART RX1                      |

|     |                 | 0         | Timer1 PWM1 Output            |

| 13  | P27 / UARTTX0   | I/O       | Port 2 pin 7                  |

|     |                 | 0         | UART TX0                      |

| 14  | P26 /           | I/O       | Port 2 pin 6                  |

|     | TIMER2PWM0      | I/O       | Timer2 PWM0 Output            |

| 15  | P25 / UARTRX0   | I/O       | Port 2 pin 5                  |

|     |                 | I         | UART RX0                      |

| 16  | P24             | I/O       | Port 2 pin 4                  |

| 17  | P23 /           | I/O       | Port 2 pin 3                  |

|     | TIMER1PWM0      | 0         | Timer1 PWM0 Output            |

| 18  | P22             | I/O       | Port 2 pin 2                  |

| 19  | P16 / SPIDO     | I/O       | Port 1 pin 6                  |

|     |                 | 0         | SPI DO                        |

| 20  | P15 / SPIDI     | I/O       | Port 1 pin 5                  |

|     |                 | I         | SPI DI                        |

| 21  | USBDM           | I/O       | USB Negative Input/Output     |

| 22  | USBDP           | I/O       | USB positive Input/Output     |

| 23  | P17 / SPICLK    | I/O       | Port 1 pin 7                  |

|     |                 | I/O       | SPI CLK                       |

| 24  | P20 / TIMER1    | I/O       | Port 2 pin 0                  |

|     |                 | I         | Timer1's External Clock Input |

### AX206 Digital Photo Frame SoC PRODUCT FACTSHEET

| 25 | P21 / TIMER0 | I/O    | Port 2 pin 1                      |

|----|--------------|--------|-----------------------------------|

|    |              | 1      | Timer0's External Clock Input     |

| 26 | P14 / BG     | I/O    | Port1 pin 4                       |

|    |              | 0      | Bandgap Output                    |

| 27 | P13 / ADC7   | I/O    | Port 1 pin 3                      |

|    |              | 1      | ADC Channel 7                     |

| 28 | P42 / PTEST  | I/O    | Port 4 pin 2                      |

|    |              | I      | Test Mode                         |

| 29 | MCLR         | I      | Master Clear Reset Input          |

| 30 | P12 / ADC6   | I/O    | Port 1 pin 2                      |

|    |              | I      | ADC Channel 6                     |

| 31 | P11 / ADC5   | I/O    | Port 1 pin 1                      |

|    |              | I      | ADC Channel 5                     |

| 32 | P10 / ADCREF | I/O    | Port 1 pin 0                      |

|    |              | I      | ADC Voltage Reference Input       |

| 33 | P30          | I/O    | Port 3 pin 0                      |

| 34 | VSS          | Ground | Negative Power Supply             |

| 35 | VDD          | Power  | Positive Power Supply             |

| 36 | P07 /        | I/O    | Port 0 pin 7                      |

|    | PORTWAKEUP   | 1      | Port Wakeup                       |

| 37 | P06 /        | I/O    | Port 0 pin 6                      |

|    | PORTWAKEUP   | I      | Port Wakeup                       |

| 38 | P05 /        | I/O    | Port 0 pin 5                      |

|    | PORTWAKEUP   | I      | Port Wakeup                       |

| 39 | P04 / ADC4   | I/O    | Port 0 pin 4                      |

|    |              | 1      | ADC Channel 4                     |

| 40 | P03 / ADC3   | I/O    | Port 0 pin 3                      |

|    |              | I      | ADC Channel 3                     |

| 41 | P02 / ADC2   | I/O    | Port 0 pin 2                      |

|    |              | I      | ADC Channel 2                     |

| 42 | P01 / ADC1   | I/O    | Port 0 pin 1                      |

|    |              | I      | ADC Channel 1                     |

| 43 | P00 / ADC0   | I/O    | Port 0 pin 0                      |

|    |              | I      | ADC Channel 0                     |

| 44 | OSC1         | 1      | Crystal Oscillator Input          |

| 45 | OSC2         | 0      | Crystal Oscillator Output         |

| 46 | OSC32K1      | 1      | 32.768K Crystal Oscillator Input  |

| 47 | OSC32K2      | 0      | 32.768K Crystal Oscillator Output |

| 48 | P37          | I/O    | Port 3 pin 7                      |

Rev 1.1.0

# 3 Memory Mapping and CPU Architecture

### 3.1 Basic Structure

AX206 CPU is modified and optimized from the standard 8051/8052 architecture. It supports most of the instructions in standard 8051/8052 except listed below:

#### DA

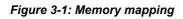

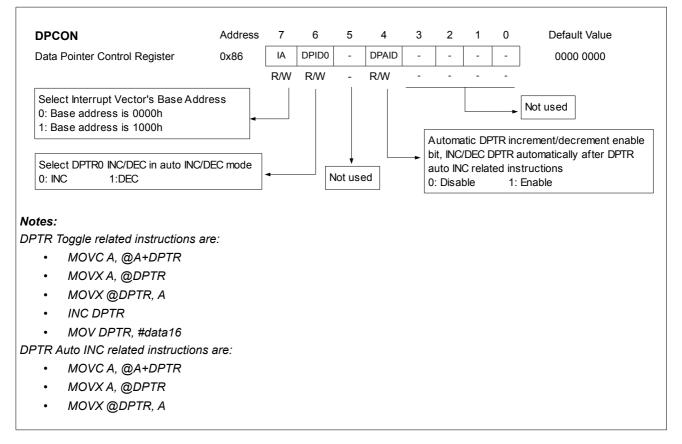

AX206 supports 1 Data Pointer Register (DPTR) for accessing the external memory space (XDATA). Also, the memory mapping is different, as shown in Figure 3-1.

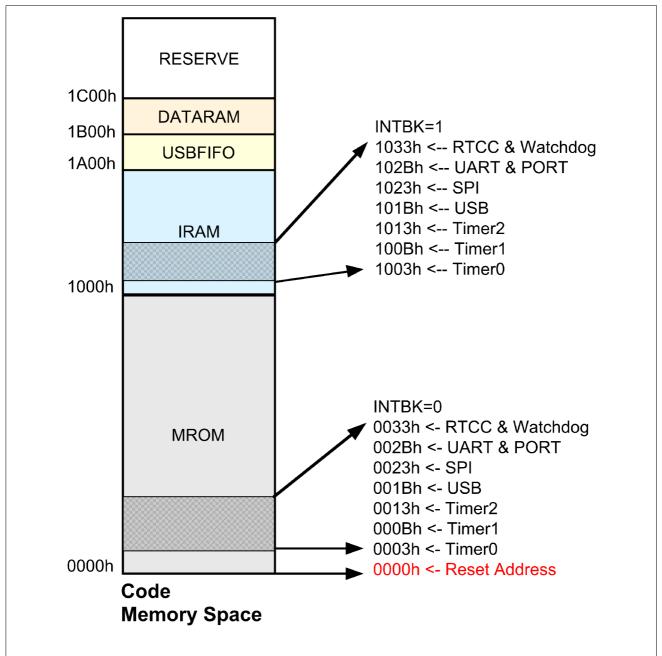

### 3.2 Interrupt Entry Address Mapping

The first instruction starts from 0000h after Power Up. That means CPU will run the boot loader program stored in MASK ROM first, and also the interrupt address is remapping start from 0003h as a standard 8051/8052. By setting the interrupt entry bank address control bit **INTBK (DPCON.7)**, the interrupt entries address will be changed starting from 1003h.

### 3.3 Data Memory – DRAM (DATA)

Data memory space (DATA) contains 256 bytes sketchpad memory, special function registers for controlling peripherals. It is also a super set of REGISTER space. To access this complex space, several addressing modes (direct, indirect, register and bit addressing) are provided. For details, please refer to the 8052 standard.

### 3.4 General Purpose Register (REGISTER)

General purpose registers *R0* through *R7* link to 32 bytes of internal data memory in the way that allows quick and efficient access. For example, the instruction *MOV A*, *00h* using two bytes of code can be replaced by shorthand notation instruction *MOV A*, *R0* that uses one byte of code only.

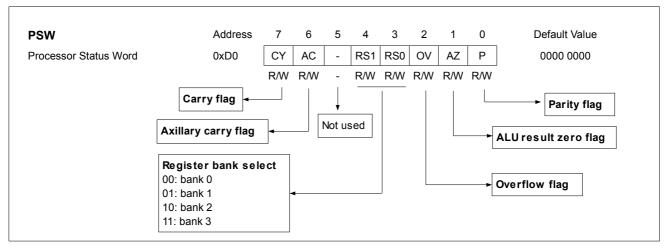

These 32 bytes of memory are put into 4 banks. Any one of them within a bank is selected by *R0* through *R7*. Desired register bank is selected using bits *RS1* and *RS0* in PSW, bit 4 and bit 3 respectively (please refer to Table 3-1 for setting description). This feature eliminates the effort required to backup the registers to stack memory during context switching, in addition provides more registers for complicated algorithms.

#### Table 3-1: Selection of Register Bank

| RS1 | RS0 | Bank | Mapping Addressing to DATA |

|-----|-----|------|----------------------------|

| 0   | 0   | 0    | 00h-07h                    |

| 0   | 1   | 1    | 08h-0Fh                    |

| 1   | 0   | 2    | 10h-17h                    |

| 1   | 1   | 3    | 18h-1Fh                    |

### 3.5 Extended Data Memory – XRAM (XDATA)

To provide a unified linear memory model, AX206 organizes internal data memory that out of the scope of DATA into extended data memory space (XDATA). Total 3K bytes of XDATA (XRAM, shared with IRAM) are addressed through instruction MOVX using a 16-bit data pointers, DPTR.

### 3.6 CPU Instruction Set Summary

### 3.6.1 Basic Instruction Set

Table 3-2 lists the basic instructions of AX206, these instruction are compatible with 8051/8052 ISA.

|      | Mnemonics     | Description                                         |

|------|---------------|-----------------------------------------------------|

| ADD  | A, Rn         | Add register to ACC                                 |

|      | A, direct     | Add direct byte to ACC                              |

|      | A, @Ri        | Add indirect byte from DRAM to ACC                  |

|      | A, #data      | Add immediate to ACC                                |

| ADDC | A, Rn         | Add register to ACC with carry                      |

|      | A, direct     | Add direct byte to ACC with carry                   |

|      | A, @Ri        | Add indirect byte from DRAM to ACC with carry       |

|      | A, #data      | Add immediate to ACC with carry                     |

| SUBB | A, Rn         | Subtract register to ACC with borrow                |

|      | A, direct     | Subtract direct byte to ACC with borrow             |

|      | A, @Ri        | Subtract indirect byte from DRAM to ACC with borrow |

|      | A, #data      | Subtract immediate to ACC with borrow               |

| INC  | A             | Increment ACC                                       |

|      | Rn            | Increment register                                  |

|      | direct        | Increment direct byte                               |

|      | DPTR          | Increment the selected DPTR                         |

|      | @Ri           | Increment indirect byte of DRAM                     |

| DEC  | A             | Decrement ACC                                       |

|      | Rn            | Decrement register                                  |

|      | direct        | Decrement direct byte                               |

|      | DPTR          | Decrement the selected DPTR                         |

|      | @Ri           | Decrement indirect byte of DRAM                     |

| MUL  | AB            | Multiply ACC and B                                  |

| DIV  | AB            | Divide ACC by B                                     |

| ANL  | A, Rn         | AND register to ACC                                 |

|      | A, direct     | AND direct byte to ACC                              |

|      | A, @Ri        | AND indirect DRAM to ACC                            |

|      | A, #data      | AND immediate to ACC                                |

|      | direct, A     | AND ACC to direct byte                              |

|      | direct, #data | AND immediate to direct byte                        |

|      | C, bit        | AND direct bit to carry                             |

|      | C, /bit       | AND complement of direct bit to carry               |

Table 3-2: Basic Instruction Set Summary

| ORL  | A, Rn              | OR register to ACC                   |

|------|--------------------|--------------------------------------|

| UNL  | A, direct          | OR direct byte to ACC                |

|      | A, @Ri             | OR indirect DRAM to ACC              |

|      | A, #data           | OR immediate to ACC                  |

|      | direct, A          | OR ACC to direct byte                |

|      | direct, #data      | OR immediate to direct byte          |

|      | C, bit             | OR direct bit to carry               |

|      | C, /bit            | OR complement of direct bit to carry |

| XRL  | A, Rn              | XOR register to ACC                  |

| ANL  | A, direct          | XOR direct byte to ACC               |

|      |                    | XOR indirect DRAM to ACC             |

|      | A, @Ri<br>A, #data | XOR immediate to ACC                 |

|      | direct, A          |                                      |

|      |                    | XOR ACC to direct byte               |

| 01.0 | direct, #data      | XOR immediate to direct byte         |

| CLR  | A                  | Clear ACC                            |

| CPL  | A                  | Complement ACC                       |

| RL   | A                  | Rotate ACC left                      |

| RLC  | A                  | Rotate ACC left through carry        |

| RR   | A                  | Rotate ACC right                     |

| RRC  | A                  | Rotate ACC right through carry       |

| SWAP | A                  | Swap nibbles of ACC                  |

| MOV  | A, Rn              | Move register to ACC                 |

|      | A, direct          | Move direct byte to ACC              |

|      | A, @Ri             | Move indirect DRAM to ACC            |

|      | A, #data           | Move immediate to ACC                |

|      | Rn, A              | Move ACC to register                 |

|      | Rn, direct         | Move direct byte to register         |

|      | Rn, #data          | Move immediate to register           |

|      | direct, A          | Move ACC to direct byte              |

|      | direct, Rn         | Move register to direct byte         |

|      | direct, direct     | Move direct byte to direct byte      |

|      | direct, @Ri        | Move indirect DRAM to direct byte    |

|      | direct, #data      | Move immediate to direct byte        |

|      | @Ri, A             | Move ACC to indirect DRAM            |

|      | @Ri, direct        | Move direct byte to indirect DRAM    |

|      | @Ri, #data         | Move immediate to indirect DRAM      |

|      | DPTR, #data        | Load DPTR with 16-bit constant       |

|      | C, bit             | Move direct bit to Carry             |

|      | bit, C             | Move Carry to direct bit             |

| MOVC | A, @A+DPTR         | Move code byte relative DPTR to ACC  |

|      | A, @A+PC           | Move code byte relative PC to ACC    |

### AX206 Digital Photo Frame SoC PRODUCT FACTSHEET

| MOVX  | A, @DPTR             | Move external data (16-bit address) to ACC          |

|-------|----------------------|-----------------------------------------------------|

|       | @DPTR, A             | Move ACC to external data (16-bit address)          |

|       | MOVX A,@Ri           | Move external data (Ri as Pointer) to ACC           |

|       | MOVX @Ri, A          | Move ACC to external data (Ri as Pointer)           |

| PUSH  | direct               | Push direct byte onto stack                         |

| POP   | direct               | Pop direct byte from stack                          |

| ХСН   | A, Rn                | Exchange register with ACC                          |

|       | A, direct            | Exchange direct byte with ACC                       |

|       | A, @Ri               | Exchange indirect DRAM with ACC                     |

| XCHD  | A, @Ri               | Exchange low nibble of indirect DRAM with ACC       |

| CLR   | С                    | Clear carry                                         |

|       | bit                  | Clear direct bit                                    |

| SETB  | С                    | Set carry                                           |

|       | bit                  | Set direct bit                                      |

| CPL   | С                    | Complement carry                                    |

|       | bit                  | Complement direct bit                               |

| JC    | rel code             | Jump if carry is set                                |

| JNC   | rel code             | Jump if carry is not set                            |

| JB    | bit, rel code        | Jump if direct bit is set                           |

| JNB   | bit, rel code        | Jump if direct bit is not set                       |

| JBC   | bit, rel code        | Jump if direct bit is set and clear bit             |

| ACALL | page code            | Absolute subroutine call                            |

| LCALL | long code            | Long subroutine call                                |

| RET   |                      | Return from subroutine                              |

| RETI  |                      | Return from interrupt                               |

| AJMP  | page code            | Absolute jump                                       |

| LJMP  | long code            | Long jump                                           |

| SJMP  | rel addr             | Short jump (relative address)                       |

| JMP   | @A+DPTR              | Jump indirect relative to DPTR                      |

| JZ    | rel code             | Jump if ACC equals zero                             |

| JNZ   | rel code             | Jump if ACC does not equal zero                     |

| CJNE  | A, direct, rel code  | Compare direct byte to ACC and jump if not equal    |

|       | A, #data, rel code   | Compare immediate to ACC and jump if not equal      |

|       | Rn, #data, rel code  | Compare immediate to Register and jump if not Equal |

|       | @Ri, #data, rel code | Compare immediate to indirect and jump if not Equal |

| DJNZ  | Rn, rel code         | Decrement Register and jump if not zero             |

|       | direct, rel code     | Decrement direct byte and jump if not zero          |

| NOP   |                      | No operation                                        |

#### Notes:

**Rn**: Register R0-R7 of the currently selected register bank.

@Ri: Data RAM location addressed indirectly through R0 or R1.

**rel code**: 8-bit, signed (2s complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

*direct*: 8-bit internal data location address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data: 8-bit immediate data

#data16: 16-bit immediate data

bit: Direct-accessed bit in Data RAM or SFR

*page code*: 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction.

*long code*: 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 64KByte program memory space.

# 4 Special Function Register (SFR)

### 4.1 SFR List

The unimplemented bits are labelled '-', never write value other than its reset value to it, otherwise unpredictable effects will be resulted. Some registers have undetermined reset value, it is labelled 'x'.

#### Table 4-1: SFR List

| Func. | Name    | Addr | Des.                                    | Reset Value |   |   |   |   |   |   |   |

|-------|---------|------|-----------------------------------------|-------------|---|---|---|---|---|---|---|

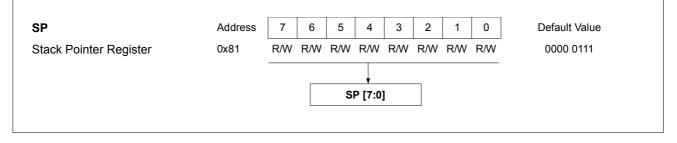

| CPU & | SP      | 81h  | Stack Pointer                           | 0           | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

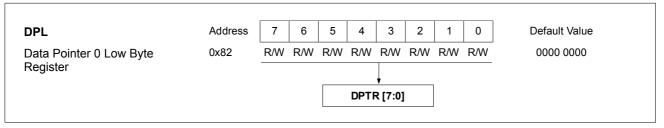

| INT   | DPL     | 82h  | DPTR0 Low byte                          | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

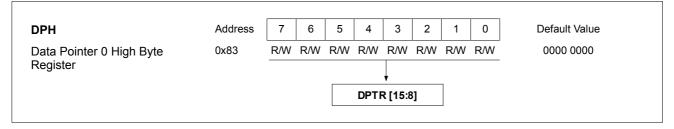

|       | DPH     | 83h  | DPTR0 High byte                         | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|       | DPCON   | 86h  | DPTR Control Register                   | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|       | IE      | A8h  | Interrupt Enable Register               | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|       | IP      | B8h  | Interrupt Priority Register             | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|       | PSW     | D0h  | Program Status Register                 | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|       | ACC     | E0h  | Accumulator                             | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|       | EIF0    | E8h  | Interrupt Flag                          | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|       | В       | F0h  | Register B                              | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| PORT  | P0      | 80h  | Port 0 Register                         | х           | x | x | x | х | x | x | x |

|       | P0DIR   | E9h  | Port 0 Direction Register               | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|       | P0UP    | F9h  | Port 0 Pull-Up Register                 | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|       | P1      | 90h  | Port 1 Register                         | х           | x | x | x | х | x | x | x |

|       | P1DIR   | EAh  | Port 1 Direction Register               | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|       | P1PU    | FAh  | Port 1 Pull-Up Register                 | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|       | P2      | A0h  | Port 2 Register                         | х           | x | x | x | х | x | x | х |

|       | P2DIR   | EBh  | Port 2 Direction Register               | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|       | P2PU    | FBh  | Port 2 Pull-Up Register                 | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|       | P3      | B0h  | Port 3 Register                         | х           | x | x | x | х | x | x | х |

|       | P3DIR   | ECh  | Port 3 Direction Register               | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|       | P3PU    | FCh  | Port 3 Pull-Up Register                 | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

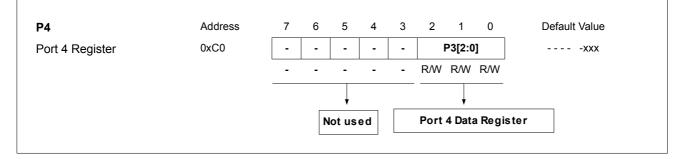

|       | P4      | C0h  | Port 4 Register                         | -           | - | - | - | - | x | x | х |

|       | P4DIR   | EDh  | Port 4 Direction Register               | -           | - | - | - | - | 1 | 1 | 1 |

|       | P4PU    | FDh  | Port 4 Pull-Up Register and PIE bit 9-8 | 1           | 1 | - | - | - | 0 | 0 | 0 |

|       | PIE     | A4h  | Port Interrupt Enable Flag              | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|       | WKPND   | 9Ah  | Port Wakeup Pending Register            | х           | x | x | x | х | x | x | х |

|       | WKEN    | 9Bh  | Port Wakeup Enable Register             | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|       | WKEDG   | 9Ch  | Port Wakeup Edge Register               | х           | x | x | x | х | x | x | x |

| SPI   | SPICON  | D8h  | SPI Control Register                    | 0           | 0 | 0 | 0 | - | 0 | 0 | 0 |

|       | SPIBAUD | D6h  | SPI Baud rate Register                  | х           | x | x | x | х | x | x | x |

|       | SPIBUF  | D7h  | SPI Buffer Register                     | х           | x | x | x | х | x | x | x |

### AX206 Digital Photo Frame SoC PRODUCT SPECIFICATION

| Func.   | Name     | Addr | Des.                                    |   |   | Re | eset | : Va | lue |   |   |

|---------|----------|------|-----------------------------------------|---|---|----|------|------|-----|---|---|

| UART    | UARTSTA  | F1h  | UART Status Register                    | 0 | 0 | 0  | 0    | -    | -   | - | 0 |

|         | UARTCON  | F2h  | UART Control Register                   | 0 | 1 | 0  | 0    | 0    | 0   | 0 | 0 |

|         | UARTBAUD | F3h  | UART Baud Rate Register                 | x | x | x  | x    | x    | x   | x | x |

|         | UARTBUF  | F4h  | UART Buffer Register                    | x | х | x  | x    | x    | x   | x | x |

| Timer   | TMR0CON  | B1h  | Timer0 Control Register                 | 0 | - | -  | -    | 0    | 0   | 0 | 0 |

|         | TMR0CNT  | B3h  | Timer0 Counter Register                 | x | x | x  | x    | x    | x   | x | x |

|         | TMR0PR   | B4h  | Timer0 Period Register                  | 1 | 1 | 1  | 1    | 1    | 1   | 1 | 1 |

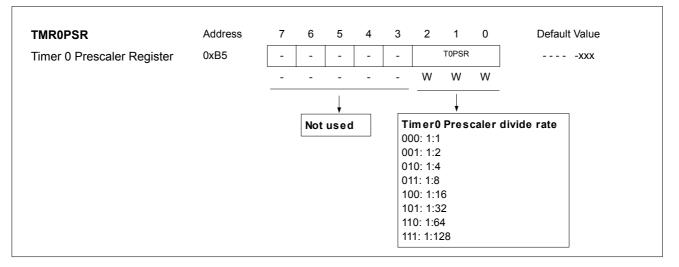

|         | TMR0PSR  | B5h  | Timer0 Prescaler Register               | - | - | -  | -    | -    | x   | x | x |

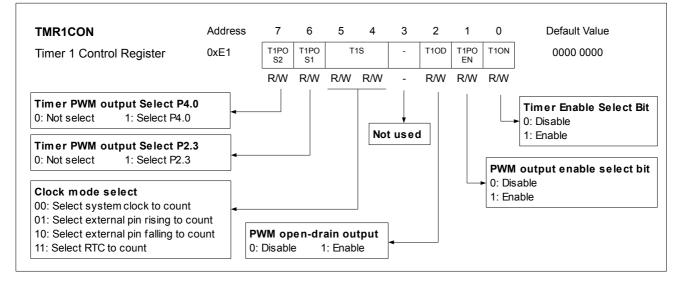

|         | TMR1CON  | E1h  | Timer1 Control Register                 | 0 | 0 | 0  | 0    | 0    | 0   | 0 | 0 |

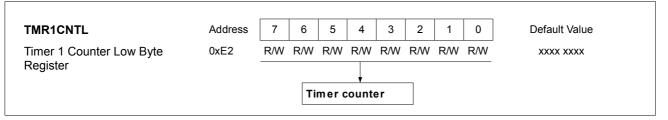

|         | TMR1CNTL | E2h  | Timer1 Counter Low Byte Register        | x | x | x  | x    | x    | x   | x | x |

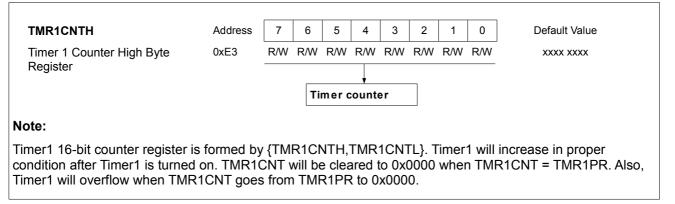

|         | TMR1CNTH | E3h  | Timer1 Counter High Byte Register       | x | x | x  | x    | х    | x   | x | x |

|         | TMR1PERL | E4h  | Timer1 Period Low Byte Register         | x | x | x  | x    | x    | x   | x | x |

|         | TMR1PERH | E5h  | Timer1 Period High Byte Register        | x | x | x  | x    | x    | x   | x | x |

|         | TMR1PWML | E6h  | Timer1 PWM Low Byte Register            | x | x | x  | x    | x    | x   | x | x |

|         | TMR1PWMH | E7h  | Timer1 PWM High Byte Register           | x | x | x  | x    | x    | x   | x | x |

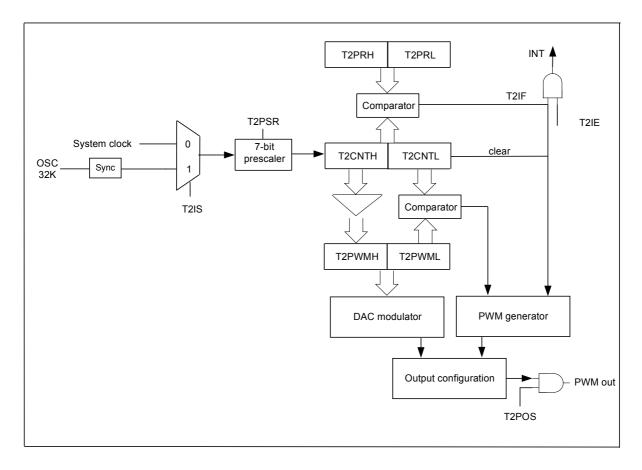

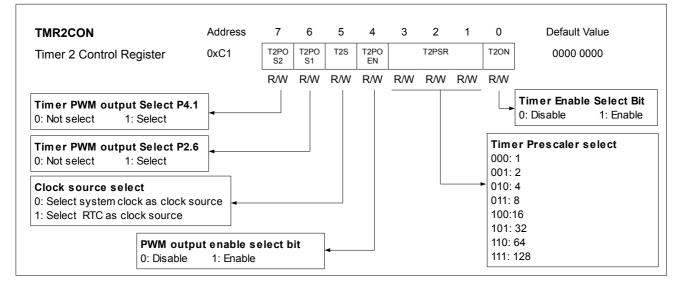

|         | TMR2CON  | C1h  | Timer2 Control Register                 | 0 | 0 | 0  | 0    | 0    | 0   | 0 | 0 |

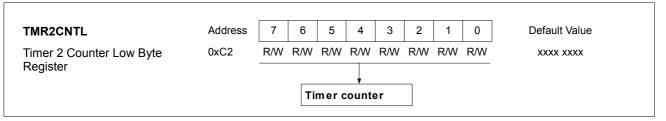

|         | TMR2CNTL | C2h  | Timer2 Counter Low Byte Register        | x | x | x  | x    | x    | x   | x | x |

|         | TMR2CNTH | C3h  | Timer2 Counter High Byte Register       | x | x | x  | x    | x    | x   | x | x |

|         | TMR2PERL | C4h  | Timer2 Period Low Byte Register         | x | x | x  | x    | х    | x   | x | x |

|         | TMR2PERH | C5h  | Timer2 Period High Byte Register        | x | x | x  | x    | x    | x   | x | x |

|         | TMR2PWML | C6h  | Timer2 PWM Low Byte Register            | x | х | x  | x    | x    | x   | x | x |

|         | TMR2PWMH | C7h  | Timer2 PWM High Byte Register           | x | x | x  | x    | x    | x   | x | x |

|         | TMR3CON  | F8h  | Timer3 (RTCC) Control Register          | 0 | 0 | 0  | 0    | -    | 0   | 0 | 0 |

|         | RTCNT    | D1h  | Timer3 (RTCC) Counter Register          | x | x | x  | x    | х    | x   | x | x |

|         | WDTCON   | BBh  | Watchdog Control Register               | 0 | 0 | 0  | 0    | 0    | 0   | 0 | 0 |

| MUL     | MULXL    | CBh  | Multiplier Operand X Low Byte Register  | x | x | x  | x    | х    | x   | x | x |

|         | MULXH    | CCh  | Multiplier Operand X High Byte Register | x | х | x  | x    | x    | x   | x | x |

|         | MULYL    | CDh  | Multiplier Operand Y Low Byte Register  | x | x | x  | x    | х    | x   | x | x |

|         | MULYH    | CEh  | Multiplier Operand Y High Byte Register | x | x | x  | x    | x    | x   | x | x |

|         | MULCON   | 98h  | Multiplier Control Register             | - | - | 0  | 0    | 0    | 0   | 0 | 0 |

|         | MULRES0  | 91h  | Multiplier Result's 0 Register          | x | x | x  | x    | x    | x   | x | x |

|         | MULRES1  | 92h  | Multiplier Result's 1 Register          | x | x | x  | x    | x    | x   | x | x |

|         | MULRES2  | 93h  | Multiplier Result's 2 Register          | x | x | x  | x    | х    | x   | x | x |

|         | MULRES3  | 94h  | Multiplier Result's 3 Register          | x | x | x  | x    | x    | x   | x | x |

| Bit-    | BFCNT    | BCh  | Bit-Fetcher Counter Register            | - | - | -  | -    | x    | x   | x | x |

| Fetcher | BFBUF0   | BDh  | Bit-Fetcher Buffer Low Byte Register    | x | x | x  | x    | x    | x   | x | x |

|         | BFBUF1   | BEh  | Bit-Fetcher Buffer Medium Byte Register | x | x | x  | x    | x    | x   | x | x |

|         | BFBUF2   | BFh  | Bit-Fetcher Buffer High Byte Register   | x | х | x  | x    | х    | x   | х | x |

### AX206 Digital Photo Frame SoC PRODUCT FACTSHEET

| Func.  | Name       | Addr | Des.                          |   |   |   | Re | set | : Va | lue |   |   |

|--------|------------|------|-------------------------------|---|---|---|----|-----|------|-----|---|---|

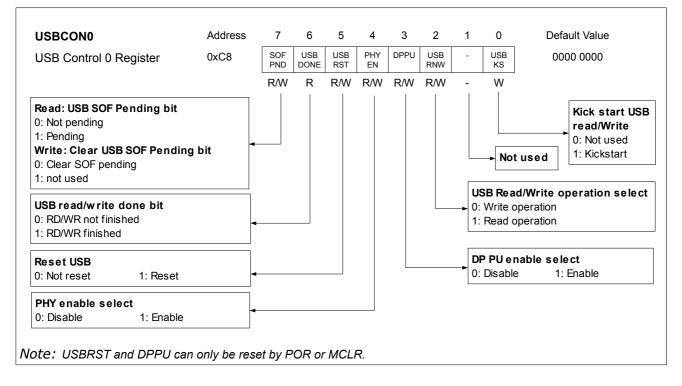

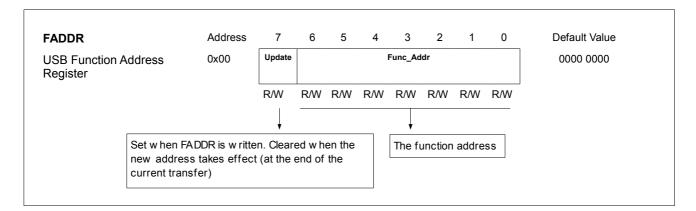

| USB    | USBCON     | C8h  | USB Control 0 Register        | ( | D | 0 | 0  | 0   | 0    | 0   | 0 | 0 |

|        | USBBUF     | C9h  | USB Buffer Register           | 2 | x | х | x  | x   | x    | x   | x | x |

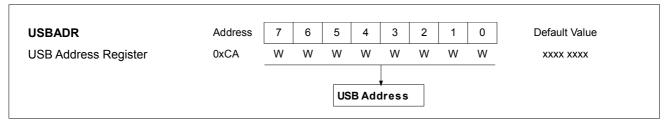

|        | USBADR     | CAh  | USB Address Register          | 3 | x | х | х  | x   | х    | x   | x | x |

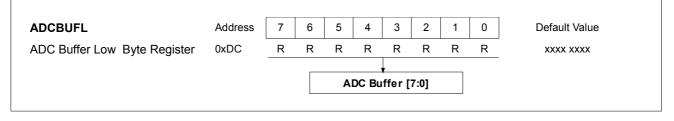

| ADC    | ADCCON     | D2h  | ADC Control Register          | ( | C | 0 | 0  | 0   | 0    | 0   | 0 | 0 |

|        | ADCBAUD    | D3h  | ADC Baud Rate Register        | ( | D | 0 | x  | x   | x    | x   | x | x |

|        | ADCBUFH    | D4h  | ADC Buffer High Byte Register | 3 | x | х | х  | x   | х    | x   | х | x |

|        | ADCBUFL    | DCh  | ADC Buffer Low Byte Register  | 3 | x | х | x  | x   | x    | x   | x | x |

| Clock  | PCON       | 87h  | Power Control Register        | ( | C | 0 | 0  | 0   | 0    | 0   | 0 | 0 |

|        | CKCON      | A5h  | Clock Control0 Register       | ( | C | 0 | 0  | 0   | 0    | 0   | 0 | 0 |

| Notes: | CREON      | ASIT |                               |   | 5 | 0 | 0  | 0   | 0    | 0   |   | , |

| : bit  | accessible |      |                               |   |   |   |    |     |      |     |   |   |

### 4.2 CPU and Interrupt SFR

#### Register 4-1: SP – Stack Pointer Register

#### Register 4-2: DPL - Data Pointer 0 Low Byte Register

### AX206 Digital Photo Frame SoC PRODUCT SPECIFICATION

#### Register 4-3: DPH - Data Pointer 0 High Byte Register

#### Register 4-4: DPCON – Data Pointer Control Register

#### Register 4-5: PSW - Processor Status Word

#### Register 4-6: ACC - Accumulator Register

| ACC |  |

|-----|--|

| ACC |  |

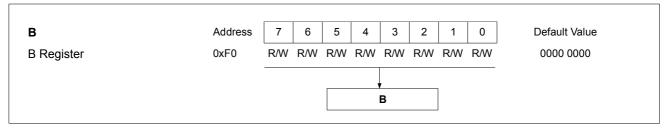

#### Register 4-7: B – B Register

# 5 Interrupt Processing

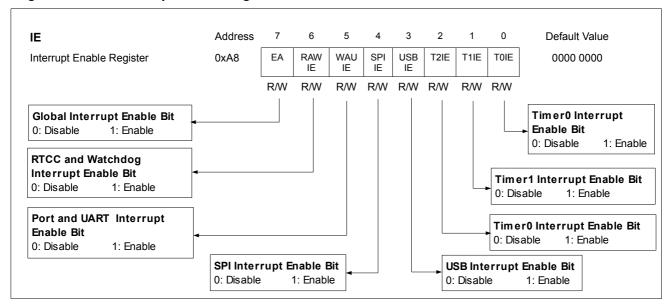

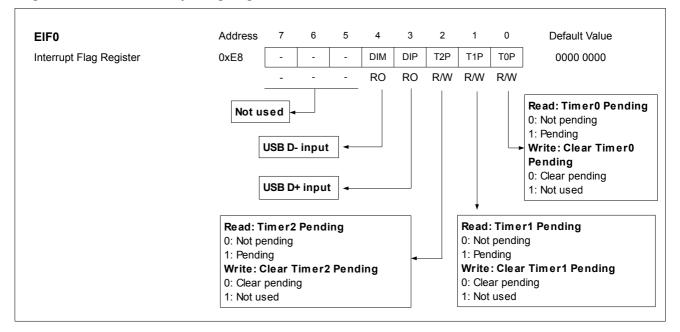

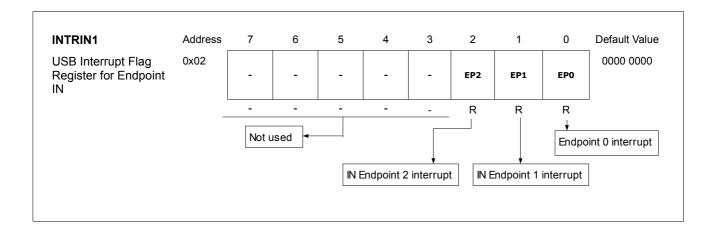

AX206 extends the interrupt system to support totally 10 interrupt sources allocating in 7 interrupt vectors with two priority levels. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupt is enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU backs up the location of the next instruction to STACK and then begins execution of an interrupt service routine (ISR). Each ISR must end with an *RETI* instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in the Interrupt Enable SFRs. However, interrupts must first be globally enabled by setting the *EA* bit (*IE.7*) to logic 1 before the individual interrupt enables are recognized.

Setting the *EA* bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings. Note that interrupts which occur when the *EA* bit is set to logic 0 will be held in a pending state, and will not be serviced until the *EA* bit is set back to logic 1.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (*RETI*) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

#### Register 5-1: IE - Interrupt Enable Register

### 5.1 Interrupt Sources and Vectors

The CPU supports 10 interrupt sources. Some interrupt sources share the same interrupt vector. Software can simulate an interrupt by setting some interrupt-pending flags to '1'. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order, and control bits are summarized in Table 5-1. Please refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

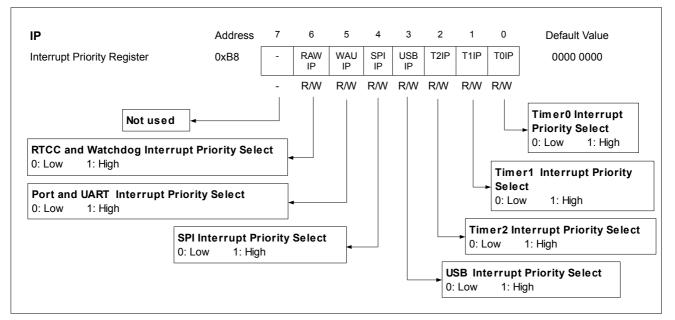

### 5.2 Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be pre-empted by a high priority interrupt. A high priority interrupt cannot be pre-empted. Each interrupt has an associated interrupt priority bit in an SFR (*IP*) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 5-1.

| Interrupt Source | Vector | Priority    | Pending Flag  | Enable Bit | Enable Bit 2  | Priority Bit |

|------------------|--------|-------------|---------------|------------|---------------|--------------|

| Timer0           | 0003h  | 1 (Highest) | EIF.0         | IE.0       | -             | IP.0         |

| Timer1           | 000Bh  | 2           | EIF.1         | IE.1       | -             | IP.1         |

| Timer2           | 0013h  | 3           | EIF.2         | IE.2       | -             | IP.2         |

| USB SOF          | 001Bh  | 4           | USBCON.7      | IE.3       | -             | IP.3         |

| USB CTL          | -      |             | N/A           |            |               |              |

| SPI              | 0023h  | 5           | SPICON.7      | IE.4       | -             | IP.4         |

| Port Wakeup      | 002Bh  | 6           | WKPND         | IE.5       | WKEN          | IP.5         |

| UART             | -      |             | UARTSTA.[7:6] |            | UARTCON[1:0]  |              |

| Watchdog         | 0033h  | 7 (Lowest)  | WDTCON.5      | IE6        | WDTCON.4/IP.7 | IP.6         |

| RTCC             |        |             | T3CON.3       |            | TMR3CON.2     |              |

#### Table 5-1: Summary of Interrupts

#### Register 5-3: IP - Interrupt Priority Register

### 5.3 Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the response time is 4–6 system clock cycles: 1 clock cycle to detect the interrupt, 2 clock cycles to back up the location of next instruction, and 1–3 clock cycles to complete the fetch and to execute the first instruction of ISR, depending on the instruction length. If an interrupt is pending when a *RETI* is executed, a single instruction is executed before serving the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an *RETI* instruction followed by a 3-byte instruction as the next instruction. In this case, the response time is 10-12 system clock cycles: 1 clock cycle to detect the interrupt, 3 clock cycles to execute the RETI, 3 clock cycles to fetch and complete the following 3-byte instruction, 2 clock cycles to back up the location of next instruction and 1–3 clock cycles to complete the fetch the first instruction of ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the *RETI* and following instruction.

# 6 Clocks and Reset Management

### 6.1 Clock System

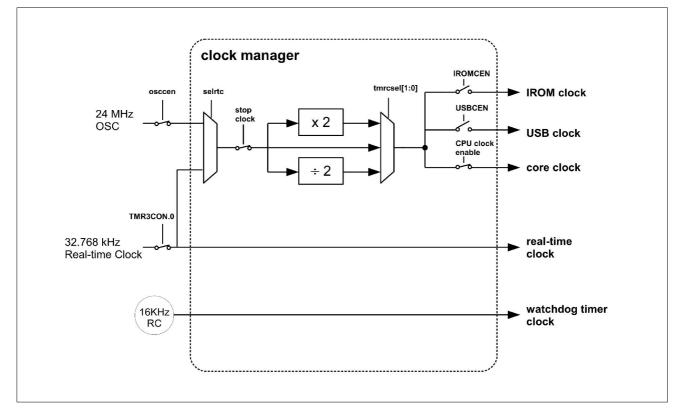

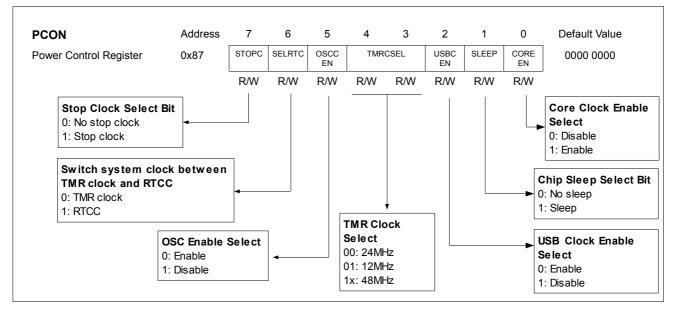

AX206 possesses a configurable clock system aiming to provide balance between performance and power consumption in different applications. It provides fine-grain clock gating to shutdown unused part completely.

Figure 6-1: Clock System Block Diagram

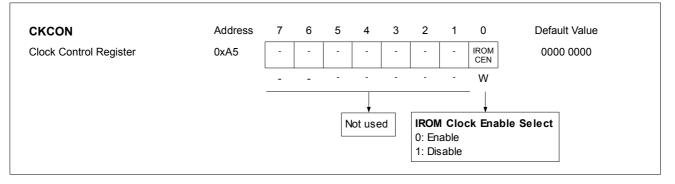

#### Register 6-2: CKCON – Clock Control Register

#### 6.1.1 Clock Source Control

Two clock domains are implemented in AX206, system clock domain and USB clock domain.

The major clock source is a high speed crystal oscillator that suits for 24MHz crystals. This clock is used directly, or is doubled, or is divided down to generate system clock for CPU and peripherals. There is another optional clock source, a 32,768 Hz crystal oscillator primarily for real-time clock, user can also choose this low speed clock source for power saving.

The selection of clock sources is controlled by setting register *SELRTC* (PCON.6). During clock switching the system clock suspends for 2 periods of the slower clock source. User must make sure the desired clock source is running before switching, otherwise the system stops which can be recovered by reset only.

#### System Clock Domain:

System clock is from either RT oscillator (32.768K clock output) or oscillator (24MHz), selected by SELRTC

(PCON.6). By default, *SELRTC* = 0 after power up and oscillator is selected for the system clock source as shown in Figure 6-1. System will run in 24MHz. By setting *TMRCSEL[1]*, the built-in x2 PLL will work to supply the clock with double frequency (48MHz) to system if needs, this example operation codes are shown as below:

//enable the x2 PLL

ORL PCON, #0x10

//insert 1 cycles delay

NOP

USB Clock Domain:

USB is inverted with System Clock. USB is enabled by default. After POR (power on reset), USB Clock run at 24MHz as well as System Clock. While connecting with USB Host, setting *TMRSEL[1]* to '1' will speed up both System Clock and USB Clock with double frequency (48MHz), setting *USBCEN* to '1' will disable USB Clock while disconnecting with USB host for saving power.

#### 6.1.2 Clock Gating Control

There are 6 bits in *PCON* and 1 bit in *CKCON* to control the clock gating for the 6 main parts in AX206, there are *COREEN (PCON.0)* for CPU, *IROMCEN (CKCON.0)* for IROM, *OSCCEN (PCON.5)* for 24MHz oscillator, *USBCEN (PCON.2)* for USB, *RTCEN (TMR3CON.0)* for RTC and *WDTEN (WDTCON.4)* for RC.

Idle Mode:

Setting *COREEN (PCON.0)* will force the CPU into a idle mode, CPU stops running instruction until any interrupts happen (EA = 1 is a must). The interrupt will wake up the CPU and CPU will go to the ISR of this interrupt source.

Stop-Clock Mode:

Setting STOPC will force the CPU into Stop-Clock mode, CPU and Peripheral will stop running until RTCC and port wakeup interrupts happen (EA = 1 is a must). The interrupt will wake up the CPU and CPU will go to the ISR of this interrupt source.

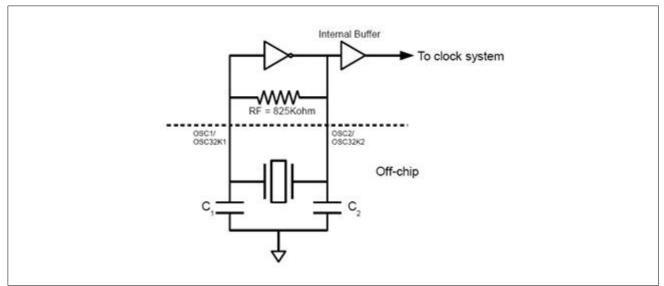

#### 6.1.3 Oscillator configurations

Table 6-1 illustrates recommended configuration of crystal/resonator oscillator at different operating frequency.  $R_F$  is the motional resistance of the crystal/resonator and can be found in crystal/resonator vendor's datasheet.  $C_1$  and  $C_2$  represents the two external loading parallel capacitors  $C_1$  and  $C_2$ .

The desired output frequency of the crystal/resonator can be fine tuned by adjusting loading capacitors  $C_1$  and  $C_2$ . The tuning range is highly dependent on crystal/resonator and users need to consult the crystal/resonator vendor for details.

#### Table 6-1: Use of $R_M$ and $C_1$ , $C_2$

| Crystal | Maximum R <sub>F</sub> (ohm) | Loading capacitor C <sub>1,</sub> C <sub>2</sub> (pF) |

|---------|------------------------------|-------------------------------------------------------|

| 32KHz   | 50K                          | 30                                                    |

| 24MHz   | 40                           | 30                                                    |

#### 6.1.4 PCB layout recommendation

Precaution should be taken when drawing printed-circuit board (PCB) layout for crystal. The crystal/resonator and the loading capacitor C1//C2 should be placed closest to AX206 OSC1/OSC2 pins and OSC32K1/OSC32K2 pins. If space is allowed, a grounded-ring surrounding the crystal and loading capacitors are always recommended in order to reduce coupling and noise from the near environment.

#### 6.1.5 RC Oscillator

The 16MHz RC oscillator is an on-chip device to supply clock for watchdog, reset circuit and oscillator stabilization circuit. It is enabled automatically when (1) watchdog is enabled; (2) CPU in reset state and (3) an oscillator is re-activated. However, RC oscillator cannot be clock source for other modules.

### 6.2 Reset System

AX206 has several different reset sources. They are grouped into 2 classifications: normal resets and induced resets. Normal resets present in typical MCUs. They are:

- 1. Master clear (External reset through pin /MCLR)

- 2. Power on reset

- 3. Watchdog timeout reset

The other type of resets is namely induced, because these are not reset source in normal operation. They reset the system due to recovery from power down mode when wakeup. The induced resets are:

- 1. Port wakeup in power down mode

- 2. Real-time wakeup in power down mode

Although the cause and condition of these 2 kinds of resets are different, they force the system to initial state in the same way. However, some registers have different reset value under different reset sources, and this is going to be discussed in the following section.

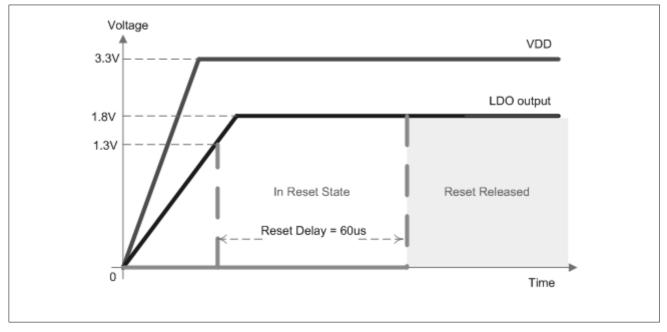

Only POR (power on reset) will reset the whole system of AX206. It's illustrated in Figure 6-3.

### 6.2.1 Reset Sequence

When the reset happens, AX206 falls back to initial state and is held. At this moment, the high speed oscillator and the RC oscillator are running. Once the reset is released, the oscillator stabilization counter starts counting. It counts for 16 ms to the oscillator becomes stable. After that, the CPU resumes and executes the first instruction located at program counter 0x0000.

#### 6.2.2 Master Reset

AX206 has a noise filter in master reset path. The filter blocks the small pulses (shorter than 8 ms) appearing at pin /MCLR.

### 6.2.3 Power On Reset

AX206 provides an on-chip Power-on Reset (POR) circuit to detect power-on and to reset internal logic before VDD reaches the pre-determined POR threshold voltage. Under VDD=3.3V, the POR threshold voltage is set to be about 2.2V.

Sometimes, when the VDD is powered off and quickly powered on again, there might be cases that the POR will work improperly and internal reset might not be generated. For this reason, AX206 POR circuit incorporates an internal self-reset module to discharge PORB output during power-off to ensure each power cycle will work properly.

### 6.2.4 Watchdog Timeout Reset

The watchdog timer (WDT) subsystem protects the microcontroller system from incorrect code execution over a long period of time by causing a system reset when the watchdog timer overflows as a result of a failure of software to feed the timer prior to the timer reaching its terminal count.

For the operation of watchdog timer, please refer to Section 8.4.

### 6.3 Power Management

#### 6.3.1 Operating in 3.3V or 5V Systems

AX206 is designed to operate in 3.3V or 5V system. It has on-chip regulator and separate supply to IO pin to guarantee seamless interfacing with 3.3V or 5V off-chip peripherals.

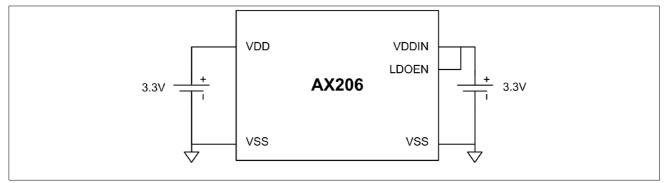

#### Operating in 3.3V System

In a 3.3V system, the on-chip regulator should be turned off by tying LDOEN to VDD. 3.3V power should be connected to both VDD and VDDIN.

#### Figure 6-4: Topology of supplying 3.3V to AX206

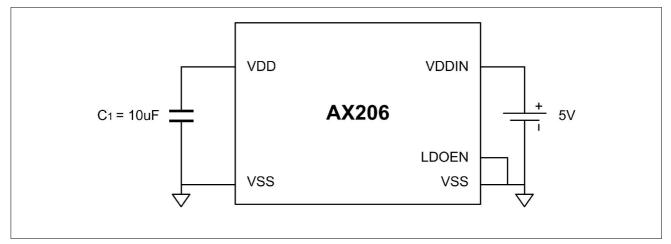

#### **Operating in 5V System**

In a 5V system, the on-chip regulator should be turned on by tying LDOEN to VSS. 5V power should be connected to VDDIN only. A capacitor should be attached to VDD and VSS to ensure good quality of on-chip regulator output.

#### Figure 6-5: Topology of supplying 5V to AX206

1. The recommended value for C1 is 10uF.

2. C1 should be placed closely to the chip.

#### 6.3.2 Idle Mode

Idle mode is the first level of power saving mode. The CPU clock stops but the rest of the clocks remains. Idle mode is activated by setting COREEN, bit 0 of PCON to '1'. Any enabled interrupt and reset sources can resume the core clock and deactivate idle mode.

#### Wakeup by enabled interrupts

| Action of CPU:          | Resumes and serves the interrupt request.                     |

|-------------------------|---------------------------------------------------------------|

| Wakeup sources:         | All enabled interrupts                                        |

| <u>Wakeup by resets</u> |                                                               |

| Action of CPU:          | Resets and serves the reset routine at program counter 0x0000 |

| Wakeup sources:         | All resets                                                    |

#### 6.3.3 Halt Mode

Halt mode aggressively shuts down the whole system clock from the "stop clock" switch showing in Figure Error: Reference source not found. At this moment, there is no activity in any module. Halt mode is activated by setting STOPC, bit 7 of PCON to '1'. Only selected interrupt and reset sources can resume the clocks and deactivate halt mode.

#### Wakeup by enabled interrupts

| Action of CPU:  | Resumes and serves the interrupt request.                                        |

|-----------------|----------------------------------------------------------------------------------|

| Wakeup sources: | Enabled watchdog interrupt, port wakeup interrupt and real-time wakeup interrupt |

#### Wakeup by disabled interrupts

| Action of CPU:          | Resumes and executes the next instruction before halt                                                                             |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Wakeup sources:         | Disabled watchdog interrupt, port wakeup interrupt and real-time wakeup interrupt (corresponding interrupt enable bit is cleared) |

| <u>Wakeup by resets</u> |                                                                                                                                   |

| Action of CPU:          | Resets and serves the reset routine at program counter 0x0000                                                                     |

| Wakeup sources:         |                                                                                                                                   |

#### 6.3.4 **Power Down Mode**

The definition of power down mode is that the whole system clock is shut down by turning off the source crystal oscillator. As AX206 has dual crystal oscillators, the condition of power down is tabulated in Table 6-2. The procedures of stopping crystal oscillators are shown in Section 6.1.2. It is recommended to disable all

peripherals and also DPLL in power down mode. Only selected interrupt and reset sources can resume the clocks and deactivate power down mode.

#### Table 6-2: Power down condition

| System clock source   | Stop high-speed oscillator | Stop 32,768 Hz oscillator |

|-----------------------|----------------------------|---------------------------|

| High-speed oscillator | Power Down mode            | Normal mode               |

| Real-time oscillator  | Normal mode                | Power Down mode           |

#### Wakeup by enabled interrupts

| Action of CPU:   | Resets and serves the reset routine at program counter 0x0000 |

|------------------|---------------------------------------------------------------|

| Wakeup sources:  | Enabled port wakeup interrupt and real-time wakeup interrupt  |

| Wakeup by resets |                                                               |

| Action of CPU:   | Resets and serves the reset routine at program counter 0x0000 |

| Wakeup sources:  | All resets                                                    |

# 7 Ports

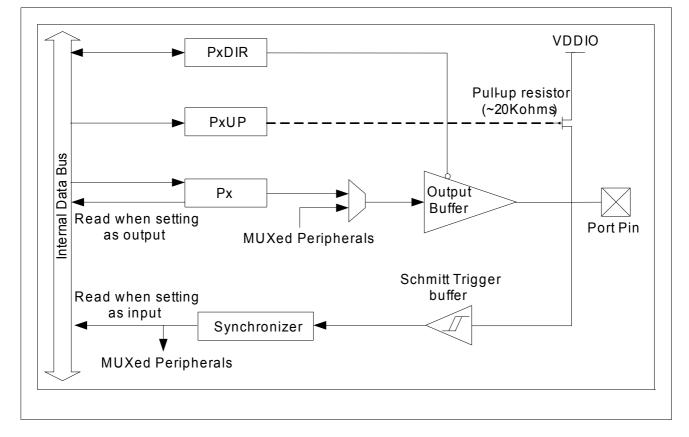

AX206 provides 4 full ports (Port0, 1, 2, 3) and a half (Port4) GPIO pins for user to develop applications. It has a total of 35 GPIO pins. Inputs are all Schmitt triggered with about 400-500mV hysteresis level to filter input voltage fluctuations. Each port pin can be independently set as input or output. Output source/sink driving strength is 8mA. Most of the port pins are built-in slew-rate controlled to reduce output bouncing noise. There is also an internally  $20K\Omega$  pull-up resistor selectable for each output port pin. Figure 7-1 shows the structure of the GPIO.

Figure 7-1: Structure of IO

٢

# 7.1 Registers

# Register 7-1: P0 - Port 0 Register

| <b>P0</b><br>Port 0 Register | Address<br>0x80 | 7   | 6   | 5        | 3<br>[ <b>7:0]</b> | 2      | 1   | 0   | Default Value |

|------------------------------|-----------------|-----|-----|----------|--------------------|--------|-----|-----|---------------|

| For o Register               | 0,00            | R/W | R/W | R/W      | <br>R/W            | R/W    | R/W | R/W | ~~~~          |

|                              |                 | •   | Ļ   | ,<br>Por |                    |        | •   | ¥   |               |

|                              |                 |     |     |          | ta Reg             | JISTEI |     |     |               |

# Register 7-2: P0DIR - Port 0 Direction Control Register

| PODIR                             | Address | 7             | 6   | 5   | 4                         | 3      | 2      | 1      | 0            | Default Value |

|-----------------------------------|---------|---------------|-----|-----|---------------------------|--------|--------|--------|--------------|---------------|

| Port 0 Direction Control Register | 0xE9    |               |     |     | P0DI                      | R[7:0] |        |        |              | 1111 1111     |

|                                   |         | R/W           | R/W | R/W | R/W                       | R/W    | R/W    | R/W    | R/W          |               |

|                                   |         | •             | •   | ł   | Ļ                         | •      | Ļ      | ļ      | $\downarrow$ |               |

|                                   |         | Port<br>0: Ou | •   |     | <b>4/3/2/1</b><br>: Input |        | ectior | 1 cont | trol bit     | :             |

|                                   |         | L             |     |     |                           |        |        |        |              |               |

# Register 7-3: P0PU - Port 0 Pull-up Register

| <b>P0PU</b><br>Port 0 Pull-up Register | Address<br>0xF9 | 7                     | 6 | 5      |                       | 3<br><b>U[7:0</b> ] |             | 1          | 0     | Default Value<br>0000 0000 |

|----------------------------------------|-----------------|-----------------------|---|--------|-----------------------|---------------------|-------------|------------|-------|----------------------------|

|                                        |                 | W                     | W | W      | W                     | w                   | W           | w          | W     | I                          |

|                                        |                 | <b>Port</b><br>0: Dis | • | 7/6/5/ | ↓<br>/4/3/2/<br>1: En | ↓<br>1/0 Pu<br>able | ↓<br>III-up | ↓<br>Enabl | e Bit |                            |

# Register 7-4: P1 - Port 1 Register

| P1              | Address | 7   | 6   | 5   |          |        | 2      | 1   | 0            | Default Value |

|-----------------|---------|-----|-----|-----|----------|--------|--------|-----|--------------|---------------|

| Port 1 Register | 0x90    |     |     |     | P1[      | 7:0]   |        |     |              | XXXX XXXX     |

|                 |         | R/W | R/W | R/W | R/W      | R/W    | R/W    | R/W | R/W          |               |

|                 |         | •   | •   | Ļ   | <b>,</b> | ţ      | Ļ      | Ļ   | $\downarrow$ |               |

|                 |         |     |     | Por | t 1 Da   | ta Reg | gister |     |              |               |

|                 |         |     |     |     |          |        |        |     |              | _             |

### Register 7-5: P1DIR - Port 1 Direction Control Register

| P1DIR                             | Address | 7                    | 6   | 5   | 4                         | 3      | 2      | 1      | 0            | Default Value |

|-----------------------------------|---------|----------------------|-----|-----|---------------------------|--------|--------|--------|--------------|---------------|

| Port 1 Direction Control Register | 0xEA    |                      |     |     | P1DI                      | R[7:0] |        |        |              | 1111 1111     |

|                                   |         | R/W                  | R/W | R/W | R/W                       | R/W    | R/W    | R/W    | R/W          |               |

|                                   |         | •                    | ţ   | ţ   | •                         | •      | Ļ      | Ļ      | $\downarrow$ |               |

|                                   |         | <b>Port</b><br>0: Ou |     |     | <b>1/3/2/1</b><br>: Input |        | ectior | n cont | rol bit      |               |

|                                   |         |                      |     |     |                           |        |        |        |              | _             |

# Register 7-6: P1PU - Port 1 Pull-up Register

| P1PU                    | Address | 7      | 6     | 5     | 4       | 3      | 2      | 1    | 0      | Default Value |

|-------------------------|---------|--------|-------|-------|---------|--------|--------|------|--------|---------------|

| Port 1 Pull-up Register | 0xFA    |        |       |       | P1P     | U[7:0] | I      |      |        | 0000 0000     |

|                         |         | W      | W     | W     | W       | W      | W      | W    | W      | -             |

|                         |         |        |       |       |         |        |        |      |        |               |

|                         |         | •      | •     | •     | •       | •      | •      |      | •      |               |

|                         |         | Port   | 1 pin | 7/6/5 | /4/3/2/ | 1/0 Pu | ıll-up | Enab | le Bit |               |

|                         |         | 0: Dis | sable |       | 1: Er   | able   |        |      |        |               |

|                         |         |        |       |       |         |        |        |      |        | ]             |

# Register 7-7: P2 - Port 2 Register

| P2              | Address | 7   | 6   | 5   | 4      | 3      | 2      | 1   | 0   | Default Value |

|-----------------|---------|-----|-----|-----|--------|--------|--------|-----|-----|---------------|

| Port 2 Register | 0xA0    |     |     |     | P2[    | 7:0]   |        |     |     | XXXX XXXX     |

|                 |         | R/W | R/W | R/W | R/W    | R/W    | R/W    | R/W | R/W |               |

|                 |         | •   | ţ   | Ļ   | Ļ      | Ļ      | Ļ      | Ļ   | Ļ   |               |

|                 |         |     |     | Por | t 2 Da | ta Reg | gister |     |     |               |

# AX206 Digital Photo Frame SoC PRODUCT SPECIFICATION

### Register 7-8: P2DIR - Port 2 Direction Control Register

| P2DIR                             | Address | 7             | 6   | 5        |                           | 3      |        | 1     | 0            | Default Value |

|-----------------------------------|---------|---------------|-----|----------|---------------------------|--------|--------|-------|--------------|---------------|

| Port 2 Direction Control Register | 0xEB    |               |     |          | P2DI                      | R[7:0] |        |       |              | 1111 1111     |

|                                   |         | R/W           | R/W | R/W      | R/W                       | R/W    | R/W    | R/W   | R/W          |               |

|                                   |         | Ţ             | ,   | <b>I</b> | Ļ                         | •      | Ļ      | ţ     | $\downarrow$ |               |

|                                   |         | Port<br>0: Ou | •   |          | <b>4/3/2/1</b><br>: Input |        | ectior | n con | trol bit     |               |

|                                   |         |               |     |          |                           |        |        |       |              |               |

### Register 7-9: P2PU - Port 2 Pull-up Control Register

| P2PU                            | Address | 7              | 6 | 5     | 4                         | 3              | 2      | 1    | 0     | Default Value |

|---------------------------------|---------|----------------|---|-------|---------------------------|----------------|--------|------|-------|---------------|

| Port 2 Pull-up Control Register | 0xFB    |                |   |       | P2P                       | U[7:0]         |        |      |       | 0000 0000     |

|                                 |         | W              | W | W     | W                         | W              | W      | W    | W     | -             |

|                                 |         |                |   |       | Ļ                         | •              |        | ļ    |       |               |

|                                 |         | Port<br>0: Dis |   | 7/6/5 | / <b>4/3/2</b> /<br>1: En | 1/0 Pu<br>able | ıll-up | Enab | e Bit |               |

### Register 7-10: P3 - Port 3 Register

| P3              | Address | 7   | 6   | 5   |        | -      | 2      | 1   | 0            | Default Value |

|-----------------|---------|-----|-----|-----|--------|--------|--------|-----|--------------|---------------|

| Port 3 Register | 0xB0    |     |     |     | P3[    | 7:0]   |        |     |              | XXXX XXXX     |

|                 |         | R/W | R/W | R/W | R/W    | R/W    | R/W    | R/W | R/W          |               |

|                 |         | Ļ   | ,   | Ļ   | ţ      | t t    | Ļ      | Ļ   | $\downarrow$ |               |

|                 |         |     |     | Por | t 3 Da | ta Reg | gister |     |              |               |

### Register 7-11: P3DIR - Port 3 Direction Control Register

| P3DIR                             | Address | 7                | 6   | 5   | 4                         | 3      | 2        | 1     | 0       | Default Value |

|-----------------------------------|---------|------------------|-----|-----|---------------------------|--------|----------|-------|---------|---------------|

| Port 3 Direction Control Register | 0xEC    |                  |     |     | P3DI                      | R[7:0] |          |       |         | 1111 1111     |

|                                   |         | R/W              | R/W | R/W | R/W                       | R/W    | R/W      | R/W   | R/W     |               |

|                                   |         | •                | •   | Ļ   | •                         | •      | <b>V</b> | ļ     | Ļ       |               |

|                                   |         | Port 3<br>0: Out | •   |     | / <b>3/2/1</b> /<br>Input | 0 dire | ction    | conti | rol bit |               |

# Register 7-12: P3PU - Port 3 Pull-up Register

| <b>P3PU</b><br>Port 3 Pull-up Register | Address<br>0xFC | 7              | 6 | 5     |       | 3<br><b>U[7:0</b> ] |        | 1    | 0      | Default Value<br>0000 0000 |

|----------------------------------------|-----------------|----------------|---|-------|-------|---------------------|--------|------|--------|----------------------------|

|                                        |                 | W              | W | W     | W     | W                   | W      | W    | W      |                            |

|                                        |                 | <b>V</b>       | Ļ | Ļ     | Ļ     | •                   | Ļ      | Ļ    | •      |                            |

|                                        |                 | Port<br>0: Dis | • | 7/6/5 | 1: En | 1/0 Pu<br>able      | ıll-up | Enab | le Bit |                            |

#### Register 7-13: P4 - Port 4 Register

### Register 7-14: P4DIR - Port 4 Direction Control Register

| P4DIR                             | Address | 7 | 6 | 5     | 4  | 3 | 2                | 1     | 0                         | Default Value      |

|-----------------------------------|---------|---|---|-------|----|---|------------------|-------|---------------------------|--------------------|

| Port 4 Direction Control Register | 0xED    | - | - | -     | -  | - | P4               | DIR[2 | :0]                       | 111                |

|                                   |         | - | - | -     | -  | - | R/W              | R/W   | R/W                       |                    |

|                                   | -       |   |   | Ļ     |    | _ |                  | ţ     | •                         |                    |

|                                   |         |   | N | ot us | ed |   | ort 4 p<br>Outpu |       | / <b>0 dire</b><br>1: Inp | ection control bit |

# AX206 Digital Photo Frame SoC PRODUCT SPECIFICATION

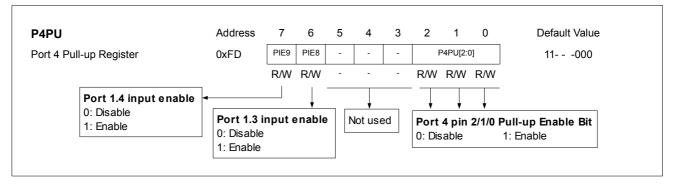

## Register 7-15: P4PU – Port 4 Pull-up Register

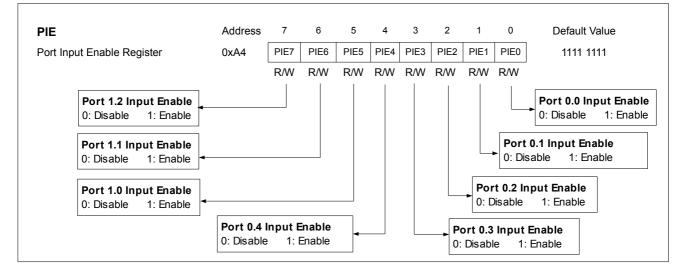

Register 7-16: PIE – Port Input Enable Register

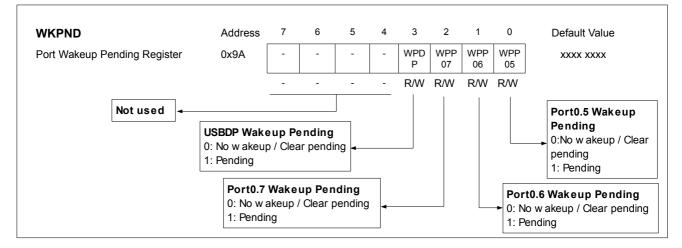

Register 7-17: WKPND – Port Wakeup Pending Register

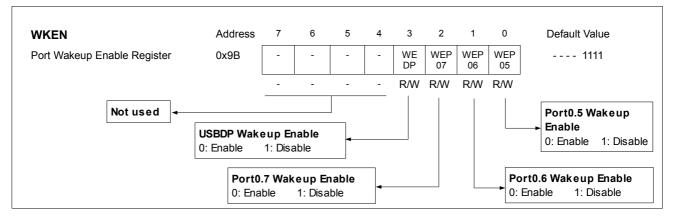

#### Register 7-18: WKEN – Port Wakeup Enable Register

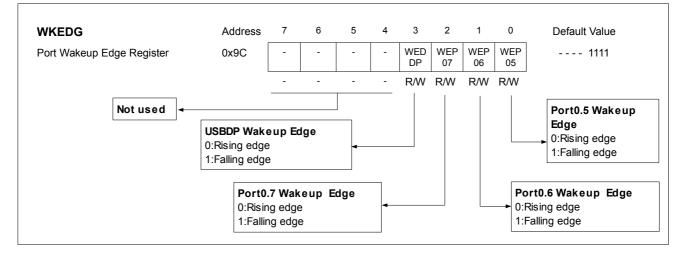

### Register 7-19: WKEDG – Port Wakeup Edge Register

# 7.2 Interrupt and Wakeup

There are 4 dedicated circuits associating with P0.5 - P0.7 and WDDP for capturing transitions at the pad. When an interested transition (defined in WKEDG) appears at the pad, these circuits generate a port wakeup interrupt pending. If the corresponding interrupt is enabled (IP[5] = 1), the interrupt request is asserted immediately to notify CPU to take action. All these circuits share the same interrupt service entry, therefore interpretation inside ISR is needed to determine the triggered circuit.

As these circuits are designed to work without clock, they are used not only for wakeup signal of idle mode, but also wakeup signal of halt mode and power down mode. For details, please refer to Section 6.3 Power Management.

These circuits are controlled by port wakeup control register, WKEN. The detecting event is defined in WKEDG. The corresponding interrupt pending flags are gathered in register WKPND.

To enable the circuit, there is an initialization procedure. User has to disable the interrupt first, and then do the setting. Before enabling the interrupt, the interrupt pending must be cleared, because false triggering is possibly happened when changing the circuit setting. Initialization must be redone in every change of setting.

# 7.3 Operation Guide

# 1. Setting Port Direction

The direction of the ports is defined in registers PxDIR. When a pin is set as output, its pull-up resistor is disabled automatically to avoid leakage current. Wrong operations like: (1) reading from an output pin results in reading out '0' only; and (2) writing to an input pin does not change the voltage level of the pad, only the corresponding port data register is changed

# 2. Reading data from and Writing data to Port

Each port of AX206 has one set of registers to manage output and input of the port. When the port is set to be output, the value of the output register Px will be reflected by the logic level of the pad.

When the port is set to be input, the logic level of the pad will be fed to the port synchronizers, and the synchronized value will be available to be read out from the input register.

# 3. Using Pull-up Registers

Each port pin associates with a 20Kohm pull-up resistor. The pull-up is disabled by default and it is enabled through register PxPU. To get rid of current leaking through the pull-up resistors, the pull-up is disabled automatically when the pin is set as output in push-pull mode and the pin outputs a low voltage level in open-drain mode. When the disabling condition is over, the pull-up setting is recovered.

# 4. Configure for Analog Input

To configure a port pin for analog peripherals, the first step is to disable the digital buffers in order to reduce interference to the analog input.

1. Set the pin to input mode